En un innovador artículo de investigación publicado hoy, los ingenieros de semiconductores de Nvidia revelaron cómo la inteligencia artificial generativa puede agilizar el complicado proceso de diseño de semiconductores. Este estudio ilustra cómo las industrias especializadas pueden aprovechar modelos de lenguaje grande (LLMs) entrenados con datos internos para desarrollar asistentes impulsados por IA, aumentando la productividad en la fabricación de semiconductores.

La investigación utilizó Nvidia NeMo, destacando el potencial de los modelos de IA personalizados para ofrecer ventajas competitivas en el sector. Diseñar semiconductores es una tarea compleja que implica la configuración precisa de chips con miles de millones de transistores en mapas de circuitos 3D que se asemejan a planos urbanos, pero son más delgados que un cabello humano. Este proceso requiere una extensa colaboración entre diversos equipos de ingeniería, cada uno centrado en diferentes aspectos del diseño y empleando herramientas de software y lenguajes de programación distintos.

Los diseñadores de chips de Nvidia desarrollaron un método para que los LLMs asistieran en la creación de chips semiconductores. El autor principal, Mark Ren, director de investigación en Nvidia, afirmó: “Creo que, con el tiempo, los modelos de lenguaje grande mejorarán procesos en todas las áreas”.

El artículo fue presentado por el científico principal de Nvidia, Bill Dally, durante una conferencia magistral en la Conferencia Internacional sobre Diseño Asistido por Computadora en San Francisco. Dally comentó: “Este esfuerzo representa un primer paso significativo en la aplicación de LLMs al complejo trabajo de diseño de semiconductores, demostrando cómo los campos especializados pueden aprovechar sus datos internos para un entrenamiento efectivo de modelos de IA generativa”.

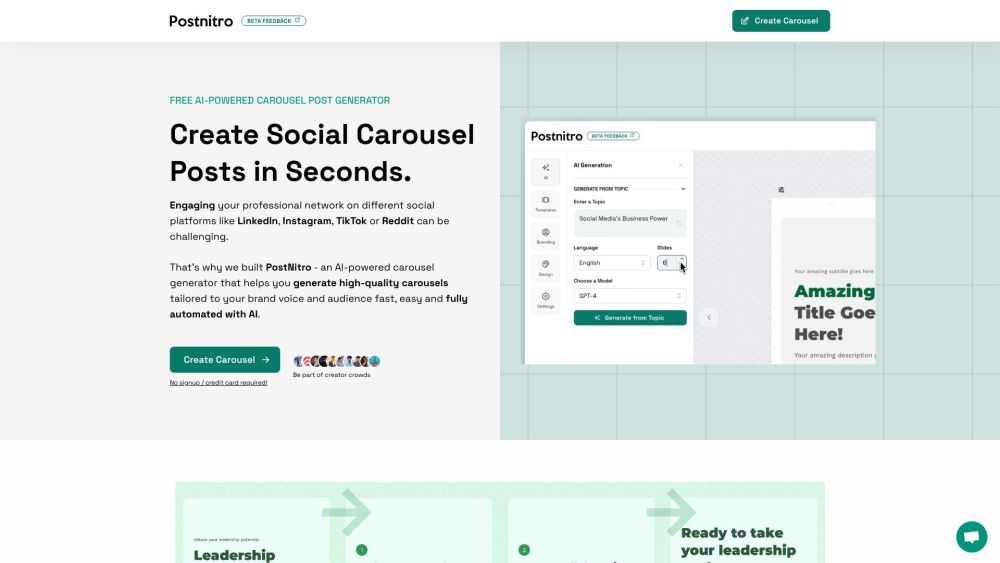

El equipo de Nvidia creó un LLM personalizado, llamado ChipNeMo, entrenado con datos internos de la empresa para generar y optimizar software, al tiempo que ayuda a los diseñadores. Su objetivo a largo plazo es implementar la IA generativa en todas las etapas del diseño de chips, mejorando significativamente la productividad. Las aplicaciones iniciales incluyen un chatbot, un generador de código y una herramienta de análisis.

La herramienta de análisis ha recibido comentarios positivos, automatizando la tediosa tarea de mantener actualizadas las descripciones de errores. Además, un prototipo de chatbot ayuda a los ingenieros a localizar rápidamente documentos técnicos, y un generador de código crea fragmentos de software especializados para diseños de chips.

La investigación subraya la dedicación del equipo a recopilar datos de diseño y crear un modelo de IA generativa adaptado a diversas industrias. Al comenzar con un modelo fundamental y utilizar Nvidia NeMo, un marco diseñado para construir, personalizar y desplegar modelos de IA generativa, refinaron el modelo final ChipNeMo, que cuenta con 43 mil millones de parámetros y fue entrenado con más de un billón de tokens. Este modelo demostró una notable capacidad para reconocer patrones.

El estudio ejemplifica cómo un equipo técnicamente capacitado puede mejorar un modelo preentrenado con sus propios datos, enfatizando la necesidad de personalizar los LLMs, ya que modelos más pequeños pueden superar a versiones más grandes de propósito general. La recopilación y limpieza de datos efectivas son fundamentales durante el proceso de entrenamiento, y se anima a los usuarios a mantenerse informados sobre las últimas herramientas que pueden optimizar sus flujos de trabajo.

A medida que la industria de los semiconductores comienza a explorar las capacidades de la IA generativa, esta investigación proporciona información crucial. Las empresas interesadas en desarrollar sus propios LLMs personalizados pueden aprovechar el marco NeMo, disponible en GitHub y en el catálogo de NVIDIA NGC.

El artículo de investigación incluye aportes de un diverso grupo de expertos, entre ellos Mingjie Liu, Teo Ene, Robert Kirby, Chris Cheng, Nathaniel Pinckney, entre otros.